- Merangkai dan Menguji operasi logika dari counter asyncronous dan counter syncronous.

- Merangkai dan Menguji aplikasi dari sebuah Counter

Senin, 12 Juni 2023

MODUL 3

Sabtu, 03 Juni 2023

LAPORAN AKHIR 1 MODUL 3

SPDT adalah singkatan dari Single Pole Double Throw. Switch jenis ini dapat menghubungkan dan memutuskan satu sambungan arus listrik pada dua arah sambungan.

4. Prinsip Kerja Rangkaian [Kembali]

7. Link Download [Kembali]

LAPORAN AKHIR 2 MODUL 3

4. Prinsip Kerja Rangkaian [Kembali]

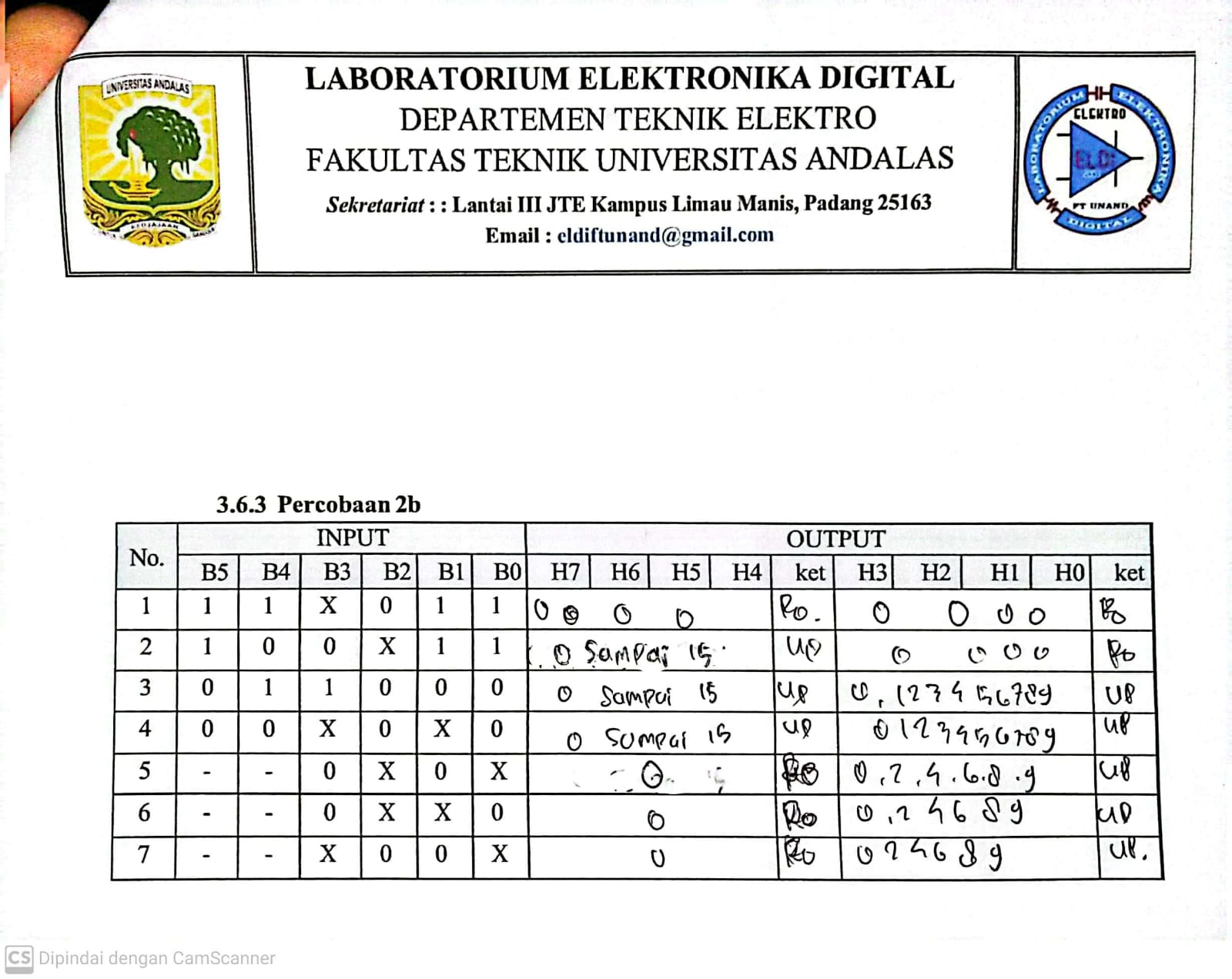

Pada percobaan ini, kita menggunakan modul D'Lorenzo dengan model DL2203D dan DL2203S. Setiap IC memiliki 6 input dan 4 output. Pada IC 74LS90, kaki B0 terhubung ke R0(1) dan kaki B1 terhubung ke R0(2). Sementara itu, kaki B2 terhubung ke R9(1) dan kaki B3 terhubung ke R9(2). Indikator untuk mengatur nilai output terletak pada input B0 dan B1. Sinyal CKA dihubungkan ke CKB dan keduanya dialiri sinyal CLOCK.

Sedangkan pada IC 7493, kaki B4 terhubung ke R0(1) dan kaki B5 terhubung ke R0(2). Pengaturan nilai output terletak pada kaki B4 dan B5. CKA dihubungkan ke CKB dan diparalelkan dengan CKA dan CKB pada IC 74LS90. Output yang dihasilkan disesuaikan dengan nilai input yang terdapat pada modul.

5. Video Rangkaian [Kembali]

TUGAS PENDAHULUAN 2 MODUL 3

4. Prinsip Kerja [Kembali]

CKA dan CKB masing-masing menerima input dari clock. R0(1) dan R0(2) masing berlogika 0, R9(1) dan R9(2) berlogika 0 dan 1. Sesuai dengan tabel diatas, maka output Q akan mangalami counter bilangan desimal secara acak yang dapat dilihat pada output berupa LED.

TUGAS PENDAHULUAN 1 MODUL 3

3. Video Simulasi [Kembali]

4. Prinsip Kerja [Kembali]

Entri yang Diunggulkan

[ MENUJU AKHIR ] [KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Pendahuluan 2. Tujuan 3. Alat dan Bahan 4. Dasar Teori 5. Perc...

-

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Tujuan 2. Alat dan Bahan 3. Dasar Teori 4. Percobaan 5. Video 6. Download Fi...

-

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Kondisi 2. Gambar Rangkaian Simulasi 3. Video Simulasi 4. Prinsip Kerja 5. Link ...

-

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Kondisi 2. Gambar Rangkaian Simulasi 3. Video Simulasi 4. Prinsip Kerja 5. Li...

.png)

.png)

.png)

.png)

.png)

.png)