3. Rangkaian Simulasi [Kembali]

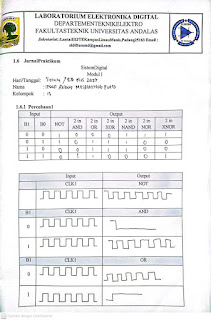

Pada percobaan kali ini, menggunakan gerbang logika yaitu NOT, AND, OR, XOR, NAND, NOR dan XNOR. Dengan prinsip nya masing masing yaitu Ketika masing masing berlogika 1, maka output dari gerbang logika masing masing adalah berbeda juga.

Ketika b1 diganti dengan clock dengan kondisi b0 berlogika 0, maka output bisa kita gambarkan grafik sinyal nya berdasarkan output yang dilihat pada simulasi ketika clock saat kondisi aktif low atau 0 maka outputnya setelah melalui gerbang logika OR adalah 0, sedangkan ketika clock naik menjadi aktif high atau 1 maka output nya adalah 1 dengan menggunakan prinsip penjumlahan sehingga untuk output sinyal nya nanti akan mengikuti bentuk sinyal clock. Begitu juga saat melewati gerbang XOR ketika clock kondisi aktif low atau 0 maka output nya adalah 0 karena 0+0 adalah genap dan ketika clock kondisi aktif high atau 1 maka output nya adalah 1 karena 0+1 adalah ganjil dan kembali lagi bentuk sinyal output nya akan mengikuti bentuk sinyal clock. Dan seterusnya untuk semua gerbang dengan mengikuti prinsip dasar gerbang logika.

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

.jpeg)

.png)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.jpeg)

.png)

.png)

.png)

.png)

Tidak ada komentar:

Posting Komentar